## EE 435

#### Lecture 18

- Moving the RHP zero into LHP in Miller Compensated Amplifier

- Breaking the Loop for Loop Gain Analysis

#### . · · · · Review from last lecture . · · · ·

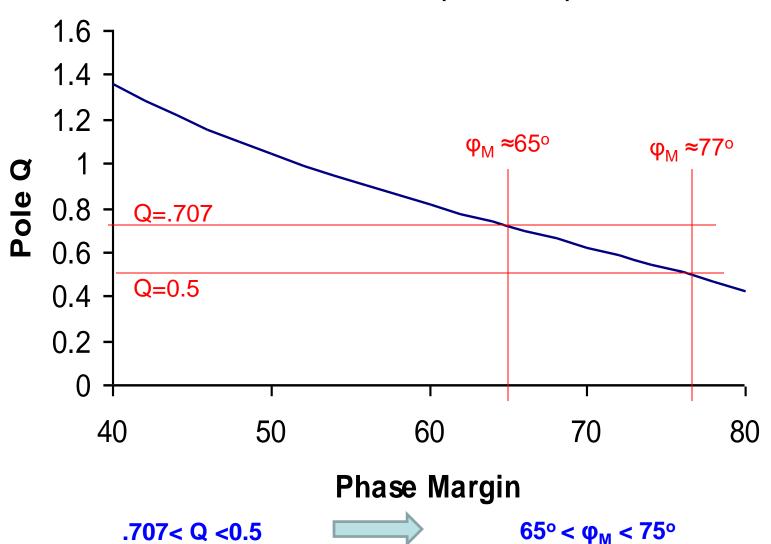

### Relationship between pole Q and phase margin

In general, the relationship between the phase margin and the pole Q is dependent upon the order of the transfer function and on the location of the zeros

In the special case that the open loop amplifier is second-order low-pass, a closed form analytical relationship between pole Q and phase margin exists and this is independent of  $A_0$  and  $\beta$ ..

$$Q = \frac{\sqrt{\cos(\phi_M)}}{\sin(\phi_M)} \qquad \qquad \phi_M = \cos^{-1}\left(\sqrt{1 + \frac{1}{4Q^4}} - \frac{1}{2Q^2}\right)$$

The region of interest is invariable only for 0.5 < Q < 0.7 larger Q introduces unacceptable ringing and settling smaller Q slows the amplifier down too much

• • • • Review from last lecture .• • • • •

### Phase Margin vs Q

Second-order low-pass Amplifier

. · · · · Review from last lecture . · · · ·

# **Compensation Summary**

- Gain and phase margin performance often strongly dependent upon architecture

- Relationship between overshoot and ringing and phase margin were developed only for 2<sup>nd</sup>-order lowpass gain characteristics and differ dramatically for higher-order structures

- Absolute gain and phase margin criteria are not robust to changes in architecture or order

- It is often difficult to correctly "break the loop" to determine the loop gain Aβ with the correct loading on the loop (will discuss this more later)

# Design of Two-Stage Op Amps

- Compensation is critical in two-stage op amps

- General approach to designing two-stage op amps is common even though significant differences in performance for different architectures

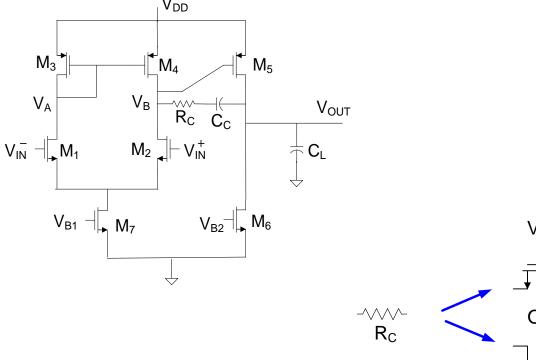

Will consider initially the most basic two-stage op amp with internal Miller compensation

#### • • • • • Review from last lecture .• • • •

# Natural Parameter Space for the Two-Stage Amplifier Design

$S_{NATURAL} = \{W_1, L_1, W_3, L_3, W_5, L_5, W_6, L_6, W_7, L_7, I_T, I_{D6}, C_c\}$

# Parameter Inter-dependence

$$A_{O} \cong \frac{g_{md}g_{mo}}{g_{oo}g_{od}}$$

$$GB \cong \frac{g_{md}}{C_{C}}$$

$$SR \cong \frac{I_{T}}{C_{C}}$$

$$g_{md} \cong \frac{1}{2}\sqrt{\mu C_{OX}\frac{W_{1}}{L_{1}}}\sqrt{I_{T}}$$

# Practical Set of Design Parameters

$$S_{PRACTICAL} = \{P, \, \theta, \, V_{EB1}, \, V_{EB3}, \, V_{EB5}, \, V_{EB6}, \, V_{EB7}\}$$

7 degrees of freedom!

- P: total power dissipation

- $\theta$  = fraction of total power in second stage

- $V_{EBk}$  = excess bias voltage for the  $k^{th}$  transistor

- Phase margin constraint assumed (so C<sub>C</sub> not shown in DoF)

• • • • Review from last lecture .• • • •

# Example for Design Procedure

Summary of Design Procedure for This Set of Specifications and this Architecture:

- 1. Choose channel length

- 2. Select: V<sub>EB3</sub>, V<sub>EB5</sub>, V<sub>EB6</sub>

- 3. Select: V<sub>FB1</sub>

- 4. Select: V<sub>EB7</sub>

- 5. Choose P to satisfy power constraint

- 6. Choose  $\theta$  to meet GB constraint

- 7. Compensation capacitance C<sub>C</sub>

- 8. Calculate all transistor sizes

- 9. Implement structure, simulate, and make modifications if necessary guided by where deviations may occur

Note: Though not shown, this design procedure was based upon looking at the set of equations that must be solved and developing a sequence to solve these equations. It may not always be the case that equations can be solved sequentially.

Note: Different specification requirements (constraints) will generally require a different design procedure

## Power distribution between stages

Note: Optimum power split for previous example was for dominant pole compensation in first stage. Results may be different for Miller compensation or for output compensation

For first-stage compensation capacitor with compensation criteria  $p_2=3\beta A_0p_1$ :

$$GB = \frac{\left(\lambda_p + \lambda_n\right)\theta P}{V_{DD}3\beta C_L}$$

For Miller Compensation with RHP zero and arbitrary Q compensation criteria:

$$GB = \frac{P(1-\theta)}{V_{DD}V_{EB1}C_{C}} = \frac{PQ^{2}(2\theta V_{EB1} - \beta(1-\theta)|V_{EB5}|)^{2}}{C_{L}\beta 2\theta V_{EB1}^{2}|V_{EB5}|V_{DD}}$$

By taking derivative of GB wrt  $\theta$ , it can be easily shown that the derivative is positive in the interval  $0<\theta\leq 1$  indicating that for a given P, want to make  $\theta$  close to 1 to maximize GB

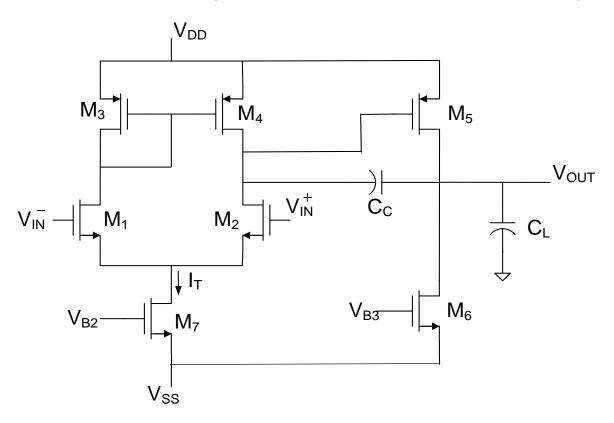

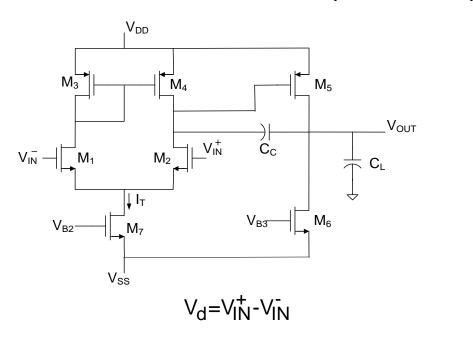

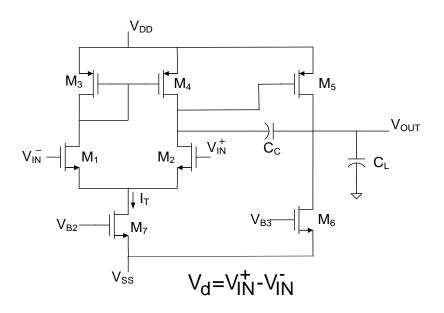

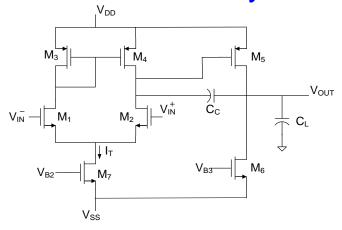

### Basic Two-Stage Op Amp

$$A_{FB}(s) \cong \frac{g_{md}(g_{m0} - sC_{c})}{s^{2}C_{c}C_{L} + sC_{c}(g_{mo} - \beta g_{md}) + \beta g_{md}g_{mo}}$$

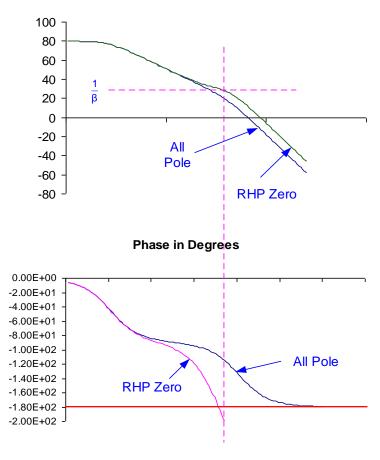

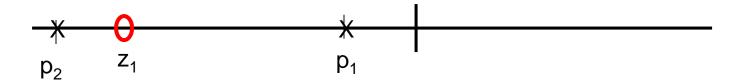

Right Half-Plane Zero Limits Performance

- Why does the RHP zero limit performance?

- Can anything be done about this problem?

- Why is this not 3<sup>rd</sup> order since there are 3 caps?

#### Why does the RHP zero limit performance?

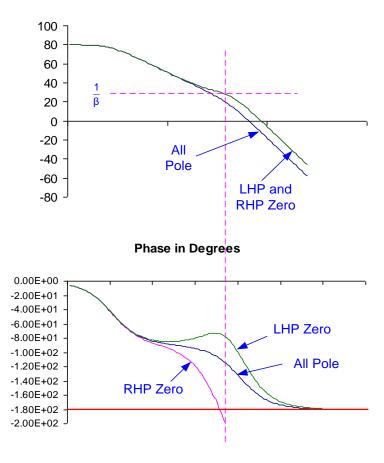

#### Gain Magnitude in dB

$$p_1 = -1$$

,  $p_2 = -1000$ ,  $z_x = \{none, +250\}$

#### In this example:

- accumulate phase shift and slow gain drop with RHP zeros

- effects are dramatic

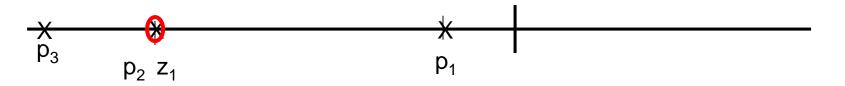

#### Why does the RHP zero limit performance?

#### Gain Magnitude in dB

$p_1=1$ ,  $p_2=1000$ ,  $z_x=\{none,250,-250\}$

#### In this example:

- accumulate phase shift and slow gain drop with RHP zeros

- loose phase shift and slow gain drop with LHP zeros

- effects are dramatic

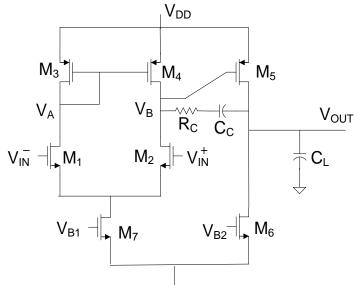

# Two-stage amplifier

(with RHP Zero Compensation)

What causes the Miller compensation capacitor to create a RHP zero?

$$A_{V} = (A_{0}p_{1}p_{2})\frac{1}{(s+p_{1})(s+p_{2})}$$

with Miller Compensation

$$A_{V} = \left(A_{0}\frac{p_{1}p_{2}}{z}\right)\frac{-s+z}{(s+p_{1})(s+p_{2})}$$

At low frequencies, V<sub>OUT</sub>/V<sub>d</sub> is positive but at high frequencies it becomes negative

Alternately, C<sub>c</sub> provides a feed-forward inverting signal from the input to the first stage output which also becomes the second stage output

Feed-forward paths create zeros in the gain transfer function!

# Two-stage amplifier

(with RHP Zero Compensation)

What can be done to remove the RHP zero?

$$A_{V} = (A_{0}p_{1}p_{2})\frac{1}{(s+p_{1})(s+p_{2})}$$

with Miller Compensation

$$A_V = \left(A_0 \frac{p_1 p_2}{z}\right) \frac{-s+z}{(s+p_1)(s+p_2)}$$

Alternately, C<sub>C</sub> provides a feed-forward inverting signal from the input to the first stage output which also becomes the second stage output

Break the feed-forward path from the output of the first stage to the output of the second stage at high frequencies

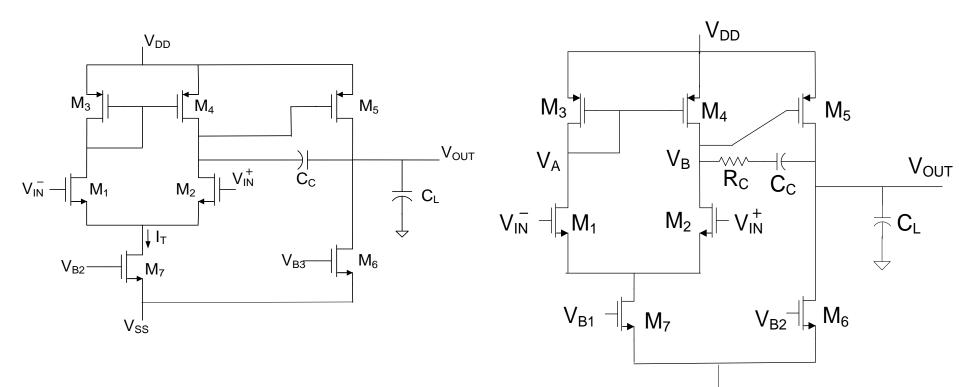

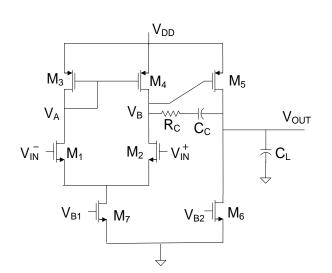

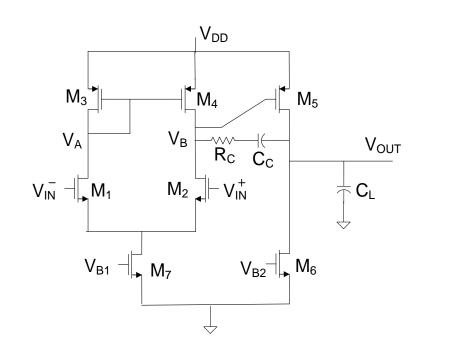

Right Half-Plane Zero Limits Performance

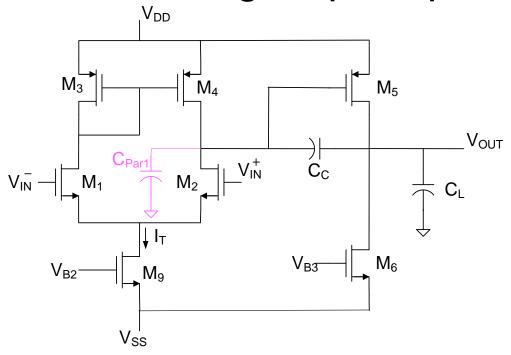

Will show zero can be moved to Left Half-Plane R<sub>C</sub> realized with single triode region device

#### Analysis almost by inspection:

$$A(s) = \frac{g_{md} \left(g_{m5} - sC_c\right)}{s^2 C_C C_L + sC_C g_{m5} + g_{oo} g_{od}}$$

$$\frac{1}{sC_c} \Rightarrow \frac{1}{sC_c} + R_c$$

$$sC_c \Rightarrow \frac{sC_c}{1 + sC_c R_c}$$

$$A(s) = \frac{g_{md} \left(g_{m5} + sC_c \left[\frac{g_{m5}}{g_c} - 1\right]\right)}{s^2 C_C C_L + sC_C g_{m5} + g_{oo} g_{od}}$$

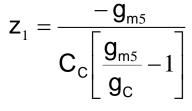

$z_{1} = \frac{-g_{m5}}{C_{c} \left[\frac{g_{m5}}{2} - 1\right]}$

$$A(s) = \frac{g_{md} \left( g_{m5} + sC_c \left[ \frac{g_{m5}}{g_c} - 1 \right] \right)}{s^2 C_c C_L + sC_c g_{m5} + g_{oo} g_{od}}$$

$$z_{1} = \frac{-g_{m5}}{C_{c} \left[ \frac{g_{m5}}{g_{c}} - 1 \right]}$$

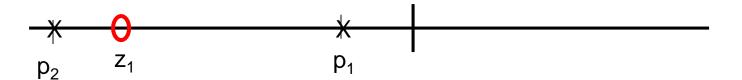

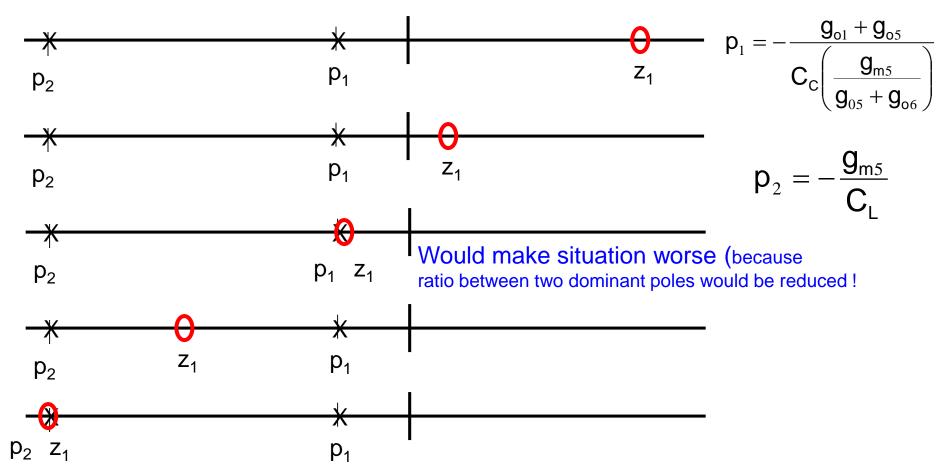

$z_1$  location can be programmed by  $R_C$  If  $g_c > g_{m5}$ ,  $z_1$  in RHP and if  $g_c < g_{m5}$ ,  $z_1$  in LHP  $R_C$  has almost no effect on  $p_1$  and  $p_2$

$$A(s) = \frac{g_{md} \left(g_{m5} + sC_c \left[\frac{g_{m5}}{g_c} - 1\right]\right)}{s^2 C_c C_L + sC_c g_{m5} + g_{oo} g_{od}}$$

$$z_1 = \frac{-g_{m5}}{C_c \left[\frac{g_{m5}}{g_c} - 1\right]}$$

$$p_{1} = -\frac{g_{o1} + g_{o5}}{C_{C} \left(\frac{g_{m5}}{g_{05} + g_{o6}}\right)} \qquad p_{2} = -\frac{g_{m5}}{C_{L}}$$

$$\mathbf{p}_2 = -\frac{\mathbf{g}_{\mathsf{m}5}}{\mathbf{C}_{\mathsf{L}}}$$

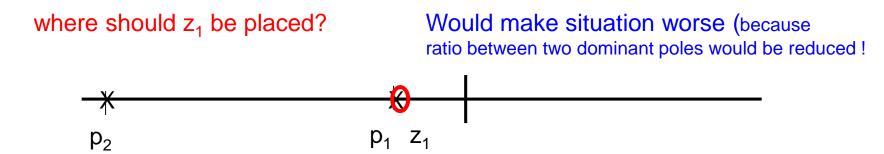

where should z<sub>1</sub> be placed?

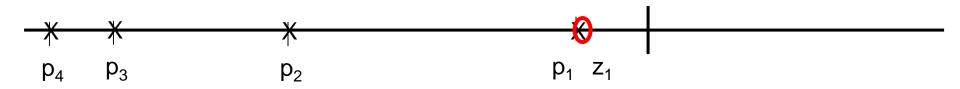

Other parasitic poles, at higher frequencies are present and not too much larger than p<sub>2</sub>!

$$z_{1} = \frac{-g_{m5}}{C_{C} \left[ \frac{g_{m5}}{g_{C}} - 1 \right]}$$

z<sub>1</sub> often used to cancel p<sub>2</sub>

Can reduce size of required compensation capacitor

- a) eliminates RHP zero

- b) increases spread between p<sub>1</sub> and p<sub>3</sub>

Improves phase margin

Design formulations easily extend to this structure

$$z_{1} = \frac{-g_{m5}}{C_{C} \left[ \frac{g_{m5}}{g_{C}} - 1 \right]}$$

Analytical formulation for compensation requirements not easy to obtain (must consider at least 3<sup>rd</sup> –order poles and both T(s) and poles not mathematically tractable)

C<sub>C</sub> often chosen to meet phase margin (or settling/overshoot) requirements after all other degrees of freedom used with computer simulation from magnitude and phase plots

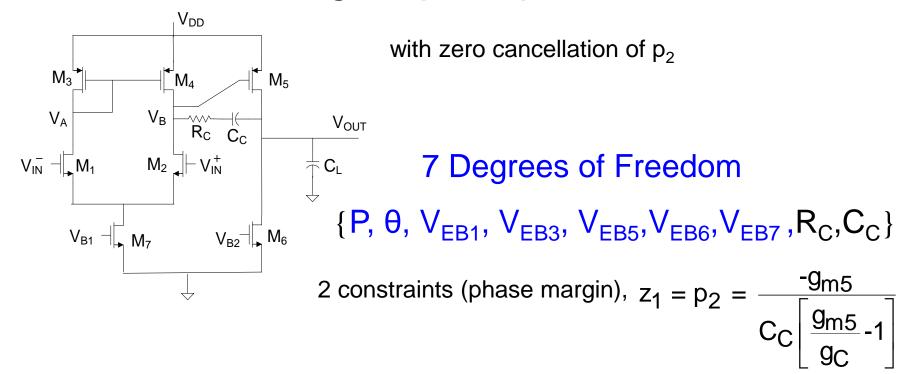

### Basic Two-Stage Op Amp with LHP zero

8 Degrees of Freedom

$$\{P, \theta, V_{EB1}, V_{EB3}, V_{EB5}, V_{EB6}, V_{EB7}, R_C, C_C\}$$

1 constraint (phase margin)

with zero cancellation of p<sub>2</sub>

7 Degrees of Freedom

{P,

$$\theta$$

,  $V_{EB1}$ ,  $V_{EB3}$ ,  $V_{EB5}$ ,  $V_{EB6}$ ,  $V_{EB7}$ ,  $R_C$ ,  $C_C$ }

2 constraints (phase margin),  $z_1 = p_2 = \frac{-g_{m5}}{C_C \left[\frac{g_{m5}}{g_C}-1\right]}$

## Basic Two-Stage Op Amp with LHP zero

### Design Flow:

- 1. Ignore R<sub>C</sub> and design as if RHP zero is present

- 2. Pick R<sub>C</sub> to cancel p<sub>2</sub>

- 3. Adjust p<sub>1</sub> (i.e. change/reduce C<sub>C</sub>) to achieve desired phase margin (or preferably desired closed-loop performance for desired β)

### Basic Two-Stage Op Amp with LHP zero

#### Realization of R<sub>C</sub>

$$R_{C} = \frac{L}{\mu C_{OX} W V_{EB}}$$

Transistors in triode region

Very little current will flow through transistors (and no dc current)

$V_{DD}$  or GND often used for  $V_{XX}$  or  $V_{YY}$

$V_{BQ}$  well-established since it determines  $I_{Q5}$

Using an actual resistor not a good idea (will not track  $g_{m5}$  over process and temp)

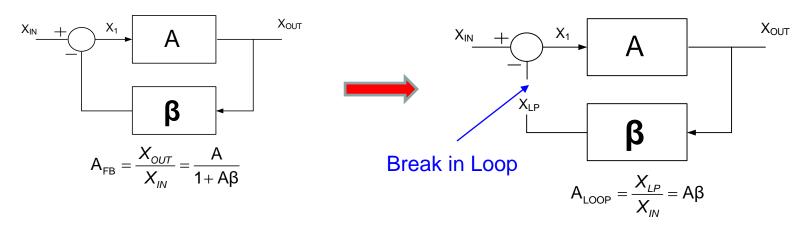

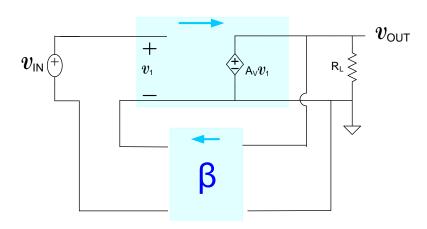

# Two-Stage Amplifiers

### Loop Gain Analysis

- Loop Gain

- Loading of A and β networks

- Breaking the Loop (with appropriate terminations)

- Biasing of Loop

- Simulation of Loop Gain

- Open-loop gain simulations

- Systematic Offset

- Embedding in closed loop

Loop Gain is a Critical Concept for Compensation of Feedback Amplifiers when Using Phase Margin Criteria (If you must!)

- Sometimes it is not obvious where the actual loop gain is at in a feedback circuit

- The A amplifier often causes some loading of the β amplifier and the β amplifier often causes some loading of the A amplifier

- Often try to "break the loop" to simulate or even calculate the loop gain or the gains A and β

- If the loop is not broken correctly or the correct loading effects on both the A amplifier and β amplifier are not included, errors in calculating loop gain can be substantial and conclusions about compensation can be with significant error

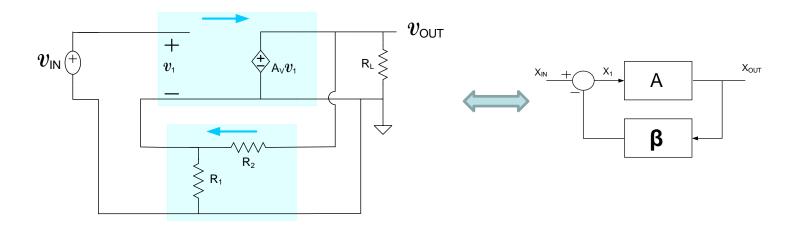

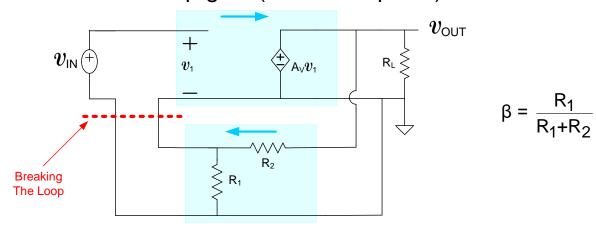

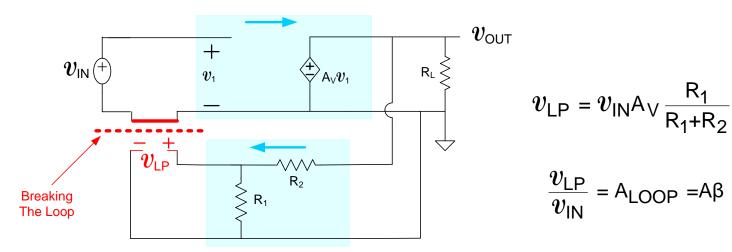

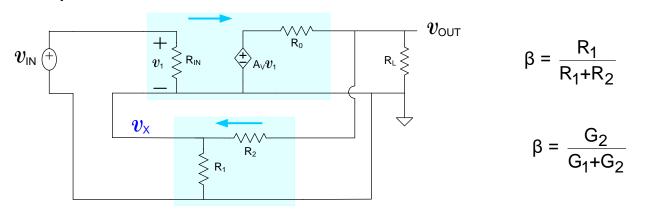

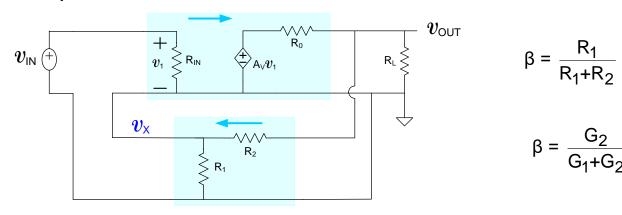

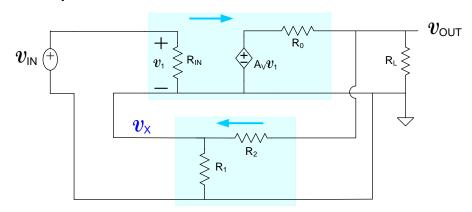

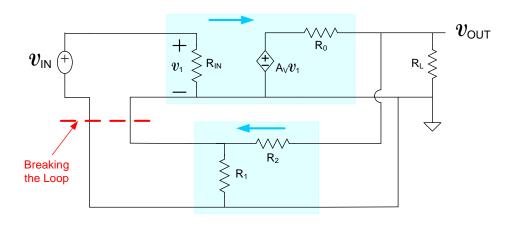

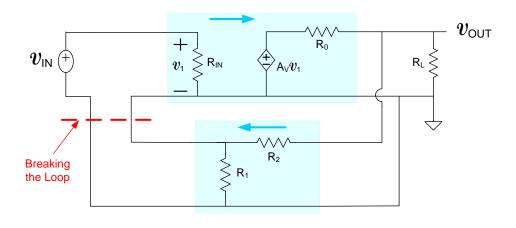

(for voltage-series feedback configuration)

The loop is often broken on the circuit schematic to determine the loop gain

Breaking the loop to obtain the loop gain (Ideal A amplifier)

Note terminations where the loop is broken – open and short

But what if the amplifier is not ideal?

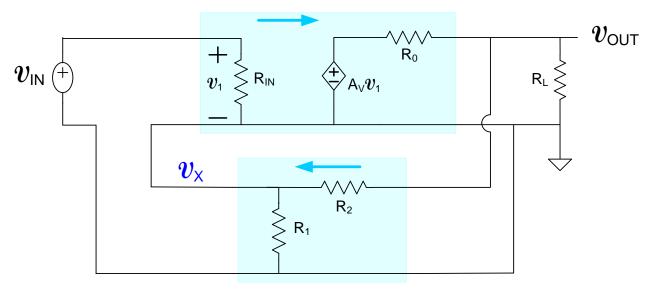

For the feedback amplifier:

$$egin{aligned} v_{\mathsf{OUT}}(\mathsf{G}_\mathsf{O} + \mathsf{G}_\mathsf{L} + \mathsf{G}_2) = & v_{\mathsf{X}} \mathsf{G}_2 + \mathsf{A}_\mathsf{V} v_{\mathsf{1}} \; \mathsf{G}_\mathsf{O} \\ v_{\mathsf{X}}(\mathsf{G}_\mathsf{1} + \mathsf{G}_\mathsf{2} + \mathsf{G}_\mathsf{IN}) = & v_{\mathsf{OUT}} \mathsf{G}_\mathsf{2} + v_{\mathsf{IN}} \mathsf{G}_\mathsf{IN} \\ v_{\mathsf{IN}} = & v_\mathsf{1} + v_{\mathsf{X}} \end{aligned}$$

Solving, we obtain

$$\mathsf{A}_{\mathsf{FB}} = \frac{v_{\mathsf{OUT}}}{v_{\mathsf{IN}}} = \frac{\mathsf{G}_{\mathsf{IN}}\mathsf{G}_2 + \mathsf{A}_{\mathsf{V}} \big(\mathsf{G}_{\mathsf{O}} \big[\mathsf{G}_1 + \mathsf{G}_2\big]\big)}{(\mathsf{G}_{\mathsf{O}} + \mathsf{G}_{\mathsf{L}})[\mathsf{G}_1 + \mathsf{G}_2 + \mathsf{G}_{\mathsf{IN}}] + \mathsf{G}_2 \big(\mathsf{G}_1 + \mathsf{G}_{\mathsf{IN}}\big) + \mathsf{A}_{\mathsf{V}} \mathsf{G}_2 \mathsf{G}_{\mathsf{O}}}$$

What is the Loop Gain? Needed to obtain the Phase Margin!

But what if the amplifier is not ideal?

$$\mathsf{A}_{FB} = \frac{v_{OUT}}{v_{IN}} = \frac{\mathsf{G}_{IN}\mathsf{G}_2 + \mathsf{A}_V \left(\mathsf{G}_O \left[\mathsf{G}_1 + \mathsf{G}_2 \right]\right)}{(\mathsf{G}_O + \mathsf{G}_L)[\mathsf{G}_1 + \mathsf{G}_2 + \mathsf{G}_{IN}] + \mathsf{G}_2 \left(\mathsf{G}_1 + \mathsf{G}_{IN}\right) + \mathsf{A}_V \mathsf{G}_2 \mathsf{G}_O}$$

What is the Loop Gain? Needed to obtain the Phase Margin!

Remember:

$$A_{FB} = \frac{F_1(s)}{1 + A\beta}$$

Characteristic Polynomial Determined by  $D(s) = 1 + A\beta$

Whatever is added to "1" in the denominator is the loop gain

But what if the amplifier is not ideal?

$$\beta = \frac{R_1}{R_1 + R_2}$$

$$\beta = \frac{G_2}{G_1 + G_2}$$

$$\mathsf{A}_{FB} = \frac{v_{OUT}}{v_{\text{IN}}} = \frac{\mathsf{G}_{\text{IN}}\mathsf{G}_2 + \mathsf{A}_{\text{V}} \big(\mathsf{G}_{\text{O}} \big[\mathsf{G}_1 + \mathsf{G}_2\big]\big)}{(\mathsf{G}_{\text{O}} + \mathsf{G}_{\text{L}}) \big[\mathsf{G}_1 + \mathsf{G}_2 + \mathsf{G}_{\text{IN}}\big] + \mathsf{G}_2 \big(\mathsf{G}_1 + \mathsf{G}_{\text{IN}}\big) + \mathsf{A}_{\text{V}} \mathsf{G}_2 \mathsf{G}_{\text{O}}}$$

Can be rewritten as

$$A_{FB} = \frac{\frac{G_{IN}G_2}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})}}{1 + A_V \left[ \frac{G_2G_O}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})} \right]}$$

The Loop Gain is

$$A_{LOOP} = A_{V} \left[ \frac{G_{2}G_{O}}{(G_{O} + G_{L})[G_{1} + G_{2} + G_{IN}] + G_{2}(G_{1} + G_{IN})} \right]$$

But what if the amplifier is not ideal?

$\beta = \frac{G_2}{G_1 + G_2}$

$$A_{LOOP} = A_{V} \left[ \frac{G_{2}G_{O}}{(G_{O} + G_{L})[G_{1} + G_{2} + G_{IN}] + G_{2}(G_{1} + G_{IN})} \right]$$

This can be rewritten as

$$\mathsf{A}_{LOOP} = \!\! \left( \mathsf{A}_{V} \! \left[ \frac{\mathsf{G}_{O} \left( \mathsf{G}_{1} \! + \! \mathsf{G}_{2} \right)}{ \left( \mathsf{G}_{O} \! + \! \mathsf{G}_{L} \right) \! \left[ \mathsf{G}_{1} \! + \! \mathsf{G}_{2} \! + \! \mathsf{G}_{|N|} \right] \! + \! \mathsf{G}_{2} \left( \mathsf{G}_{1} \! + \! \mathsf{G}_{|N|} \right)} \right] \! \right) \! \left[ \frac{\mathsf{G}_{2}}{\mathsf{G}_{1} \! + \! \mathsf{G}_{2}} \right]$$

This is of the form

$$A_{LOOP} = (A_{VL}) \left[ \frac{G_2}{G_1 + G_2} \right]$$

where  $A_{VL}$  is the open loop gain including loading of the load and  $\beta$  network!

$$A_{VL} = A_{V} \left[ \frac{G_{O}(G_{1}+G_{2})}{(G_{O}+G_{L})[G_{1}+G_{2}+G_{IN}]+G_{2}(G_{1}+G_{IN})} \right]$$

But what if the amplifier is not ideal?

$$\beta = \frac{R_1}{R_1 + R_2}$$

$$\beta = \frac{G_2}{G_1 + G_2}$$

The Loop Gain is

$$\mathsf{A}_{LOOP} = \mathsf{A}_{V} \left[ \frac{\mathsf{G}_{2} \mathsf{G}_{O}}{(\mathsf{G}_{O} + \mathsf{G}_{L})[\mathsf{G}_{1} + \mathsf{G}_{2} + \mathsf{G}_{IN}] + \mathsf{G}_{2}(\mathsf{G}_{1} + \mathsf{G}_{IN})} \right]$$

The Forward Amplifier Gain is

$$A_{VL} = A_V \left[ \frac{G_O(G_1 + G_2)}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})} \right]$$

Note that A<sub>VL</sub> is affected by both its own input and output impedance and that of the β network

This is a really "messy" expression

Any "breaking" of the loop that does not result in this expression for  $A_{v_l}$  will result in some errors though they may be small

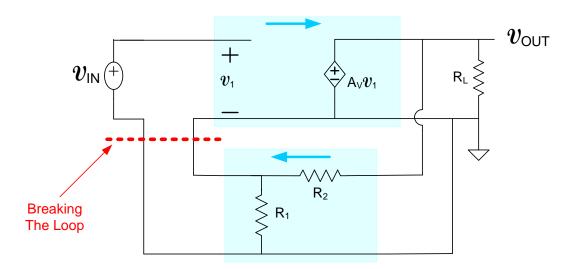

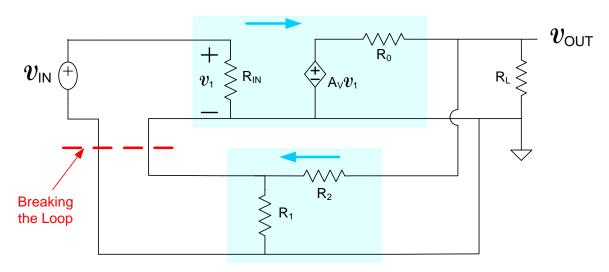

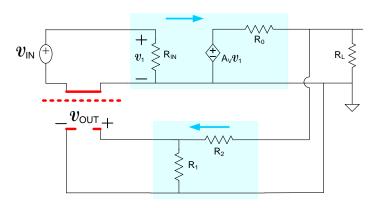

(for voltage-series feedback configuration)

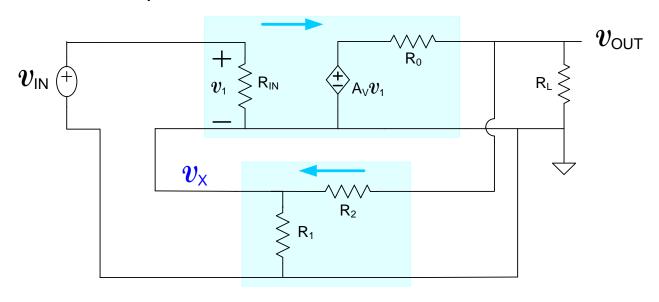

But what if the amplifier is not ideal?

- Most authors talk about breaking the loop to determine the loop gain Aβ

- In many if not most applications, breaking the loop will alter the loading of either the A amplifier or the β amplifier or both

- Should break the loop in such a way that the loading effects of A and  $\beta$  are approximately included

- Consequently, breaking the loop will often alter the actual loop gain a little

- Q-point must not be altered when breaking the loop (for analysis with simulator)

- In most structures, broken loop only gives an approximation to actual loop gain

- Sometimes challenging to break loop in appropriate way

(for voltage-series feedback configuration)

#### But what if the amplifier is not ideal?

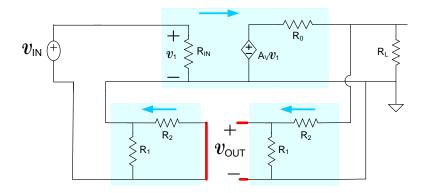

Standard Loop Gain Circuit including Biasing

(terminations shown in ss circuit are what is needed in the actual amplifier)

(for voltage-series feedback configuration)

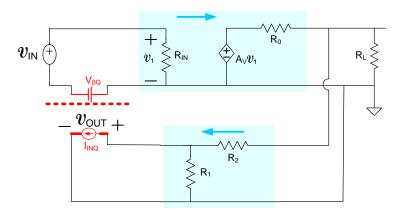

#### But what if the amplifier is not ideal?

$$\mathsf{A}_{LOOP} = \mathsf{A}_V \Bigg[ \frac{\mathsf{G}_2 \mathsf{G}_O}{\big(\mathsf{G}_O + \mathsf{G}_L\big) \big[\mathsf{G}_1 + \mathsf{G}_2\big] + \mathsf{G}_2 \big(\mathsf{G}_1\big)} \Bigg]$$

Loop Gain from Terminated Loop

$$\begin{split} A_{LOOP} = A_V & \left[ \frac{G_2 G_O}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})} \right] \\ & \qquad \qquad \text{Real Loop Gain} \end{split}$$

Breaking loop even with this termination will result in some error in A<sub>LOOP</sub>

(for voltage-series feedback configuration)

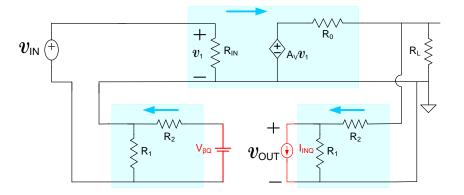

#### But what if the amplifier is not ideal?

#### Better Loop Gain Circuit including Biasing

Better Standard Small-Signal Loop Gain Circuit

(terminations shown in ss circuit are what is needed in the actual amplifier)

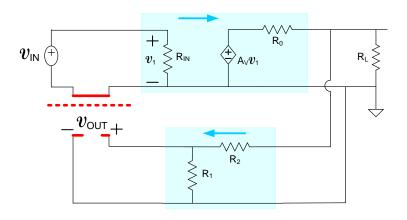

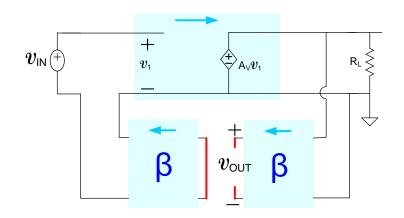

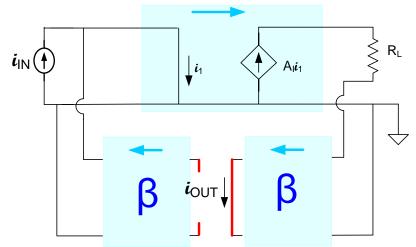

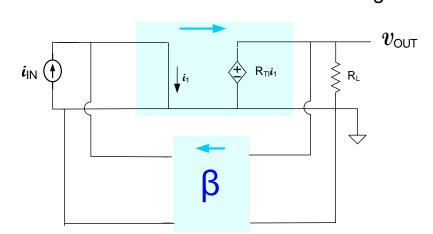

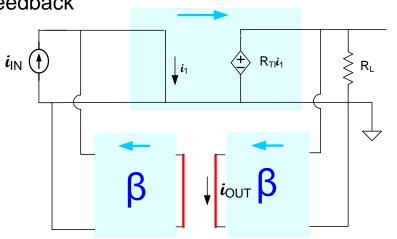

#### for four basic amplifier types

voltage-series feedback

#### **Feedback Amplifier**

#### **Loop Gain Amplifier**

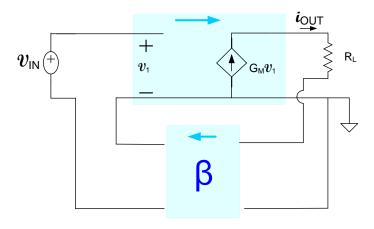

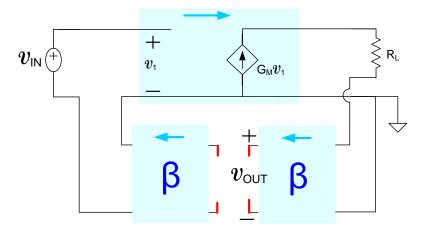

#### current-series feedback

#### for four basic amplifier types

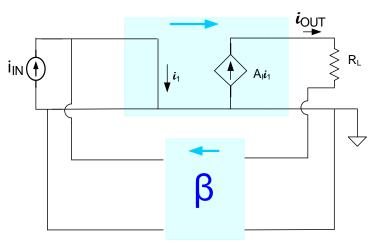

#### current-shunt feedback

#### Feedback Amplifier

Loop Gain Amplifier voltage-shunt feedback

Stay Safe and Stay Healthy!

# End of Lecture 18